Rivalul SK Hynix lucrează și la NAND cu 400 de straturi

De ce contează: Tehnologia V-NAND de la Samsung a avansat semnificativ, crescând de la 24 de straturi la aproape 300 de straturi în puțin peste un deceniu. Deși compania s-a confruntat cu provocări semnificative în ceea ce privește scalarea suplimentară, rămâne încrezătoare că poate potrivi cel puțin 400 de straturi de celule de memorie flash în cipurile NAND. Dacă totul decurge conform planului, producția de masă ar putea începe până la sfârșitul anului viitor.

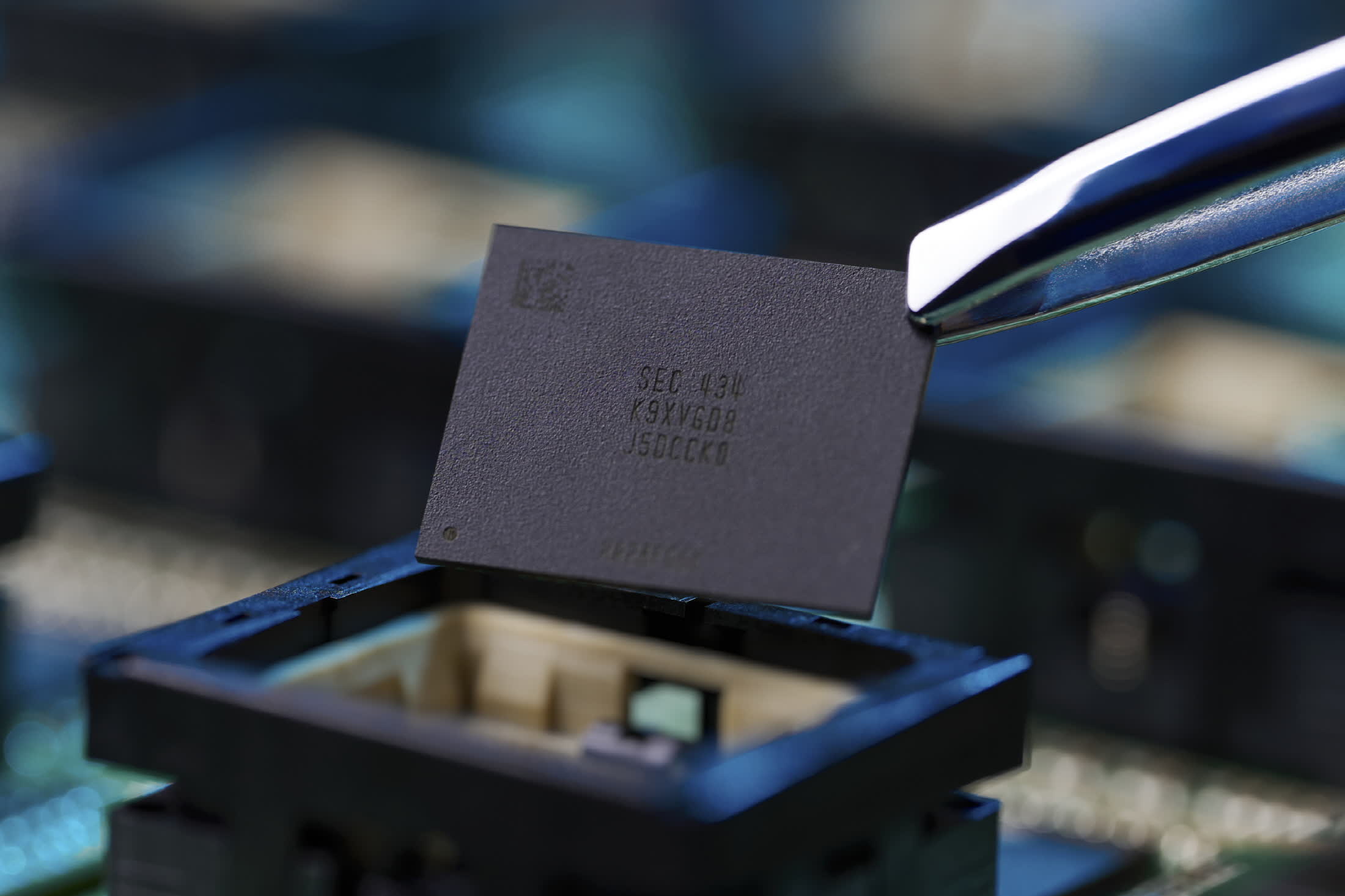

Memoria flash V-NAND de 280 de straturi Samsung de generația a 9-a a intrat abia recent în producția de masă, primele produse comerciale fiind așteptate să ajungă pe rafturile magazinelor anul viitor. Cu toate acestea, potrivit Korea Economic Daily, compania stabilește deja obiective ambițioase pentru tehnologia sa V-NAND cu 400 de straturi de a 10-a generație.

Concurența în spațiu s-a intensificat în ultimii ani, determinată în mare parte de cerințele tot mai mari ale aplicațiilor AI, împreună cu un apetit tot mai mare al consumatorilor pentru stocare flash mai mare și mai accesibilă.

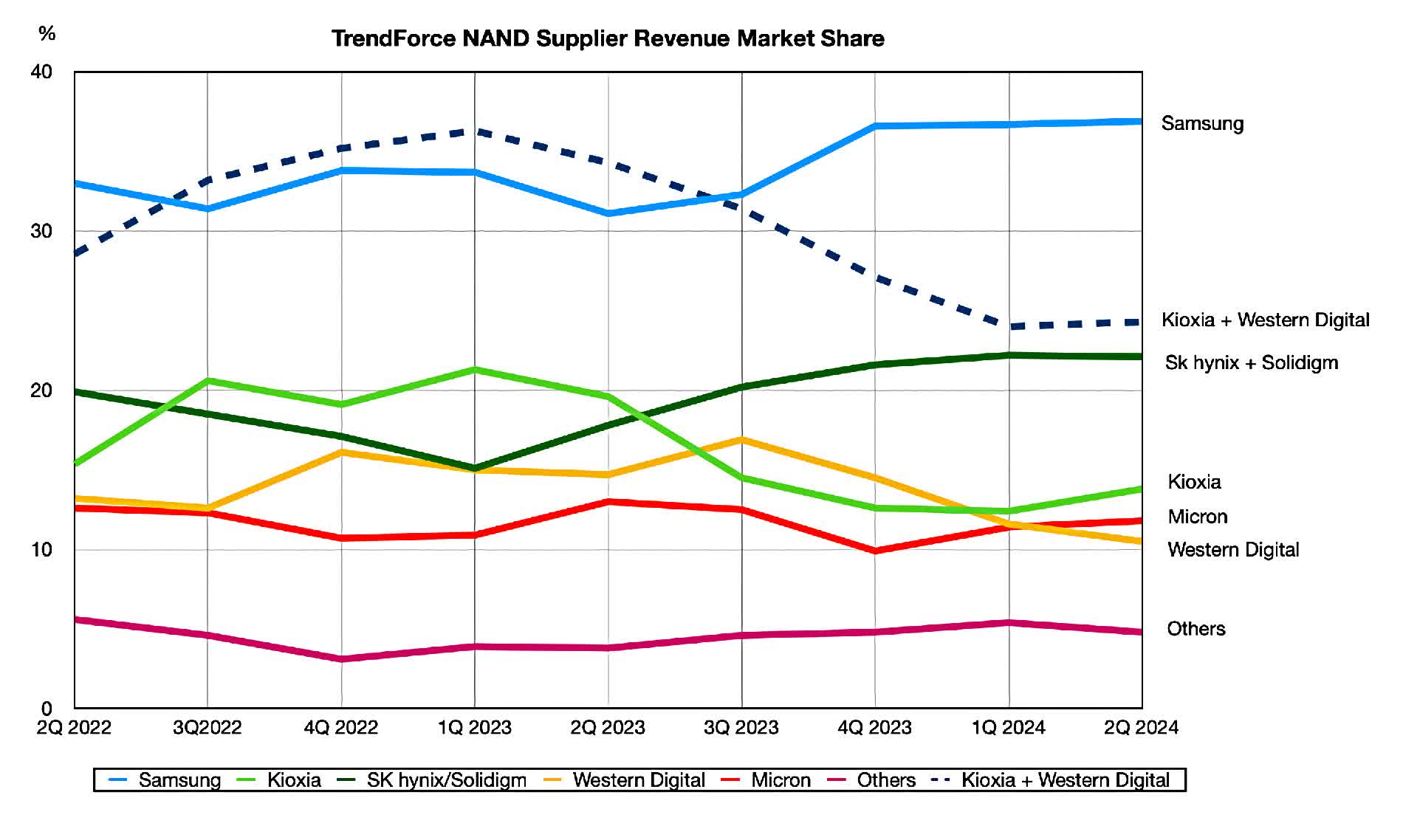

Samsung deține în prezent o cotă de piață de 37%, dar menținerea acestei poziții devine din ce în ce mai dificilă, deoarece concurenți precum Micron, YMTC, SK Hynix și Kioxia își accelerează dezvoltarea 3D NAND cu densitate mai mare.

SK Hynix intenționează să înceapă producția de NAND cu 400 de straturi până la sfârșitul anului 2025, producția la scară largă fiind așteptată în prima jumătate a anului 2026. Acest lucru a determinat Samsung să vizeze aceeași cronologie, deoarece rivalul său mai mic coreean a câștigat o cotă de piață semnificativă peste ultimii doi ani.

Stivuirea a 400 sau mai multe straturi de NAND nu este o operație ușoară, deoarece scalarea peste 300 de straturi a pus deja provocări pentru fiabilitatea prototipurilor timpurii. Pentru a rezolva acest lucru, Samsung intenționează să folosească o arhitectură Tri-Level Cell (TLC) alături de o nouă tehnologie numită Bonding Vertical NAND (BV NAND), care separă celulele de memorie și circuitele periferice pe diferite wafer-uri, care sunt apoi legate între ele într-o structură verticală. .

Această abordare va ajuta, de asemenea, Samsung să obțină randamente de producție mai mari în comparație cu cele ale designului NAND Cell over Periphery (CoP). Compania susține că poate atinge densități de 28 Gb/mm² sau 1 Tb (128 GB) pe matriță, care este doar puțin mai mică decât densitatea obținută cu o arhitectură Quad-Level Cell (QLC) de a 9-a generație. În plus, rata de date de 5,6 Gb/s per pin oferă o creștere semnificativă a performanței față de maximul de 3,2 Gb/s atins cu designul anterior.

În teorie, viitoarele SSD-uri Samsung ar putea atinge capacități de până la 16 TB, cu viteze care se apropie de limitele unei interfețe PCIe 5.0 x4 în citiri și scrieri secvențiale.

Samsung va prezenta această nouă arhitectură promițătoare V-NAND mai detaliat la viitoarea Conferință Internațională de Circuite Solid-State din februarie 2025.