Scopul este de a aduce pe piață pachete multi-chiplet care depășesc un trilion de tranzistori până în 2030.

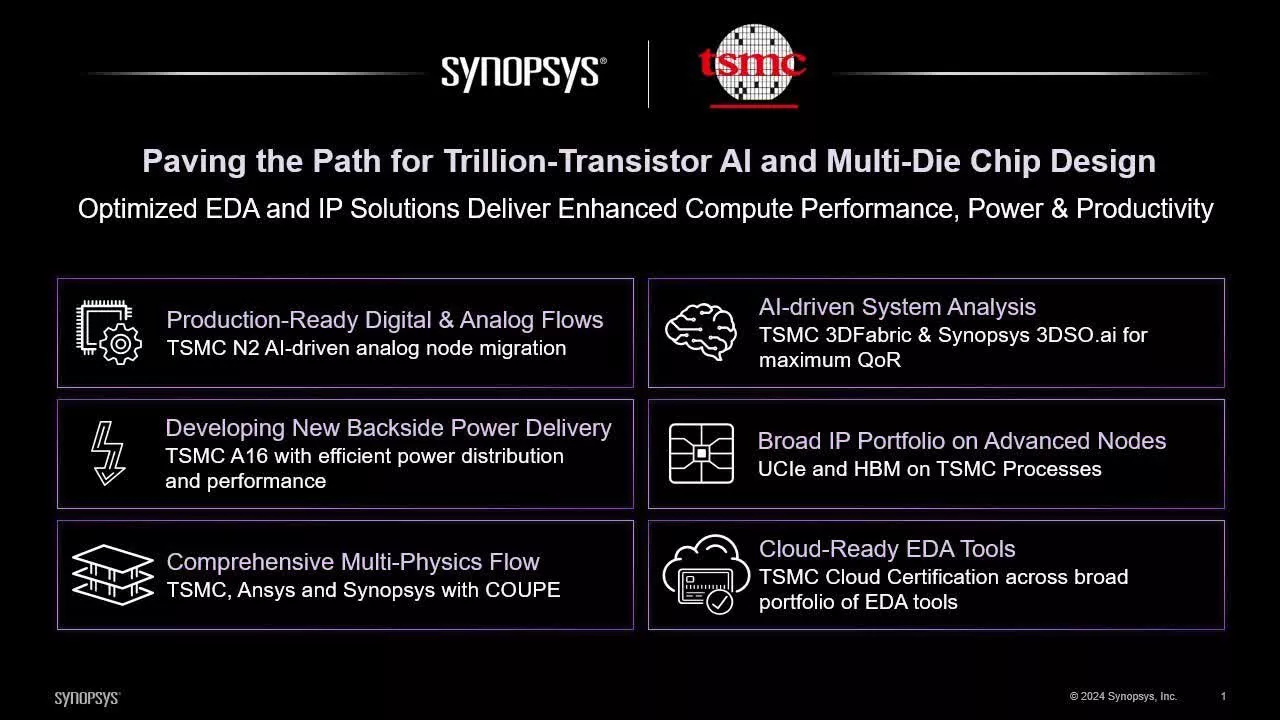

Pe scurt: Synopsys și TSMC lucrează împreună de zeci de ani, iar un nou anunț arată că își duc parteneriatul la următorul nivel pentru a alimenta cererea pentru mai multă putere de calcul AI. Synopsys a dezvăluit că își aliniază îndeaproape suita EDA alimentată de AI și soluțiile multi-die cu cele mai recente noduri de proces și tehnologia de ambalare 3D ale TSMC. Scopul este de a deschide calea pentru proiecte care împachetează miliarde sau chiar trilioane de tranzistori.

Pentru cei neinițiați, EDA înseamnă Electronic Design Automation. Este un set de instrumente software pentru proiectarea sistemelor electronice, cum ar fi cipurile cu circuite integrate. Pe acest front, instrumentele de proiectare și simulare personalizate ale Synopsys, certificate pentru nodul N2 al TSMC, plătesc deja dividende pentru MediaTek.

Potrivit lui Ching San Wu de la MediaTek, fluxul EDA stimulat de AI le permite designerilor lor analogici să maximizeze performanța și eficiența pe N2, accelerând în același timp timpul necesar pentru a-și livra SoC-urile pe piață.

Synopsys a dezvăluit, de asemenea, că soluțiile sale de verificare și implementare fizică acceptă acum rutarea din spate pe procesul A16 al TSMC. A16 este cel mai avansat nod de proces al TSMC vreodată, programat să fie produs în masă în a doua jumătate a anului 2026. Rutarea din spate este o tehnologie în curs de dezvoltare care direcționează liniile de alimentare pe partea din spate a unui cip sau a unui circuit integrat în loc de partea frontală obișnuită. Acest lucru ajută la optimizarea livrării de energie și direcționarea semnalului pentru o performanță și o densitate mai bune.

Synopsys adaugă că instrumentele sale au fost certificate în cloud de TSMC pentru a simplifica și mai mult procesul de proiectare. Acest lucru le permite „clienților reciproci” să acceseze resursele cloud EDA precise pentru sarcini precum sinteza, aspectul personalizat, simularea și verificarea semnării.

Pe frontul multi-die, platforma Synopsys 3DIC Compiler a fost îmbunătățită prin colaborarea cu Ansys și TSMC. Platforma 3DIC Compiler oferă practic un mediu unificat pentru proiectarea, implementarea și verificarea pachetelor complexe 2.5D și 3D multi-die. Cu cea mai recentă actualizare, efectuează analize de temporizare termică și conștientă de infraroșii în integrare strânsă cu platforma de semnare RedHawk a Ansys.

Merită menționat faptul că TSMC a schițat o foaie de parcurs pentru cipuri de trilioane de tranzistori și la conferința International Electron Devices Meeting (IEDM) de anul trecut, urmată de o altă versiune în mai. Compania a stabilit 2030 ca țintă pentru nodurile de proces A14 de 1,4 nm și A10 de 1 nm. În paralel, s-a vorbit despre dezvoltarea tehnologiilor avansate de ambalare precum CoWoS, InFO și SoIC. Aceste tehnologii vor permite împreună pachete gigantesche multi-chiplet care depășesc un trilion de tranzistori în jurul anului 2030. Odată cu acest nou anunț, producătorul de cipuri pare să se apropie de obiectivul său.