Eforturile necesită ani de dezvoltare înainte de a câștiga tracțiune comercială

Ceva de așteptat: Industria memoriei este cunoscută pentru abordarea sa conservatoare, favorizând adesea îmbunătățirile incrementale față de schimbările revoluționare. Dar, pe măsură ce privim spre sfârșitul deceniului, se pare că lumea va vedea apariția DRAM-ului stivuit monolitic 3D. Singurele întrebări care rămân sunt ce formă va lua și când va fi gata pentru producția în masă.

În timp ce memoria flash a făcut progrese semnificative în ceea ce privește capacitatea prin procesarea 3D monolitică, DRAM s-a confruntat cu provocări în realizarea unei arhitecturi 3D similare. Obstacolul principal a fost necesitatea unui mijloc suficient de mare de stocare a sarcinii, de obicei sub forma unui condensator.

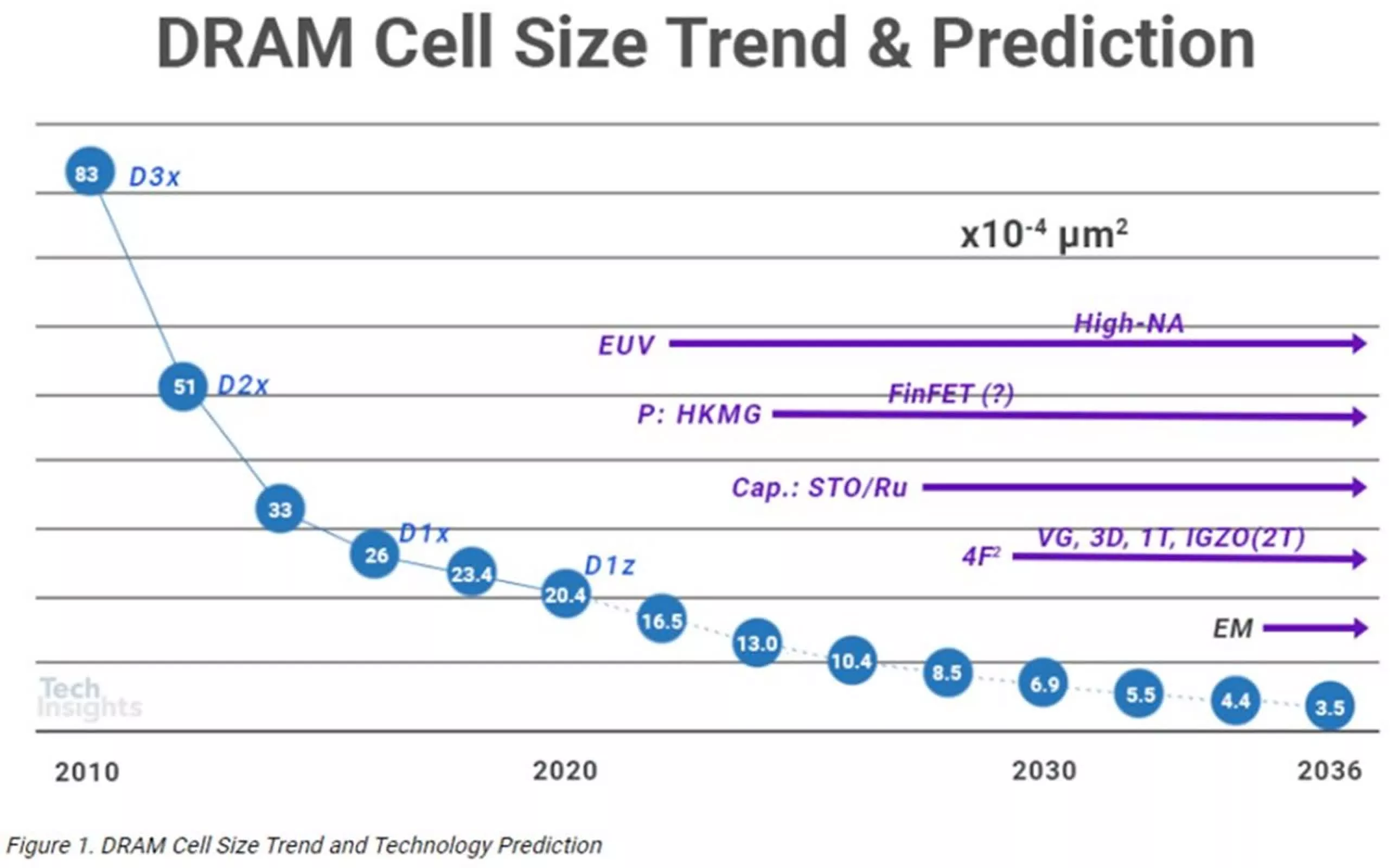

Cea mai simplă abordare pentru creșterea stocării de date pe un cip DRAM cu un singur strat este reducerea dimensiunii celulei. Cu toate acestea, condensatorul vertical din modelele tradiționale DRAM creează straturi foarte groase, ceea ce face dificilă stivuirea. Pentru a rezolva acest lucru, unele eforturi sunt concentrate pe rularea condensatoarelor pe orizontală, în timp ce altele vizează eliminarea totală a condensatorului.

„DRAM urmează pașii NAND, evoluând la trei dimensiuni pentru a construi mai mult spațiu de stocare pe unitate de suprafață”, a declarat Benjamin Vincent, senior manager la nivel mondial al proceselor și integrării semiconductoarelor la Lam Research. „Acest lucru este bun pentru industrie, deoarece împinge limitele tehnologice pentru memorie și pentru că mai mulți biți pe micrometru pătrat înseamnă că costurile de producție scad.”

Este important de reținut că 3D DRAM se poate referi la două concepte distincte. Unul deja în producție este memoria cu lățime de bandă mare (HBM). Cu toate acestea, HBM este o memorie stivuită, nu o matriță monolitică, cum ar fi flash-ul 3D NAND.

Dezvoltarea unui cip DRAM 3D monolitic ar putea oferi un impuls imediat dacă este folosit în arhitectura HBM, a declarat Daryl Seitzer, director de produs principal pentru memoriile încorporate la Synopsys, pentru Semiconductor Engineering. „Când DRAM 3D viabil din punct de vedere comercial este disponibil și provocările legate de stivuirea matrițelor, cum ar fi managementul termic, au fost abordate în continuare, aceasta ar fi o veste bună pentru furnizorii HBM, deoarece introduce îmbunătățiri ale densității memoriei și ale eficienței energetice care vor avea impact pentru centrele de date și aplicațiile AI.” spuse el.

O abordare pentru optimizarea celulelor DRAM implică micșorarea dimensiunilor caracteristicilor prin tehnici avansate de litografie. Cei mai recenti pași către reducerea amprentei opune modelarea EUV cu procesele tradiționale ArF SADP și SAQP pentru DRAM 2D de ultimă oră, conform lui Daniel Soden, manager de dezvoltare a afacerii la Brewer Science.

Samsung lucrează la o nouă arhitectură de celule care își propune să atingă o eficiență a zonei de 4F2 (unde F este dimensiunea minimă a caracteristicii). Acest design folosește un tranzistor cu canal vertical și trece de la celula actuală 6F2 la 4F2. Cu toate acestea, va necesita materiale noi, inclusiv feroelectrice, și precizie ridicată pentru a construi.

O altă direcție promițătoare implică așezarea condensatorului pe o parte pentru a crea straturi mai subțiri, potrivite pentru stivuire. Lam Research a propus mai multe idei pentru a realiza acest lucru, inclusiv răsturnarea celulei, alunecarea liniei de biți și folosirea tranzistorilor GAA (gate-all-around). „Experții în gravare și depunere ar putea fi șocați de ceea ce propun simulările noastre”, a spus Vincent. „De exemplu, șanțurile cu dimensiuni critice de 30 nm și adâncime de 2 µm sunt considerate a fi gravate și umplute în arhitectura noastră”.

Cercetătorii explorează, de asemenea, modele DRAM fără condensator. O alternativă implică tiristoare controlate de poartă, în timp ce alta folosește un corp plutitor similar cu poarta plutitoare utilizată în memoria flash. Neo Semiconductor a propus o tehnologie comercială care folosește o celulă cu corp plutitor cu dual gate. „Pe baza simulărilor, acest mecanism poate crește marja de detectare și retenția datelor”, a spus Andy Hsu, CEO și co-fondator al Neo Semiconductor.

Deși aceste progrese sunt promițătoare, este important de reținut că DRAM 3D nu este chiar după colț. Toate eforturile actuale vor necesita mulți ani de dezvoltare și evaluare înainte ca acestea să aibă tracțiune comercială. „Noile arhitecturi sunt întotdeauna mai dificile decât implementarea metodologiilor existente”, a spus Soden.